Table of Contents

1.半導体の種類

半導体(半導体デバイス)は、その機能、集積度、材料など、さまざまな視点から分類できます。最も一般的で実用的な用途・機能による分類と、近年特に重要な材料による分類を説明します。

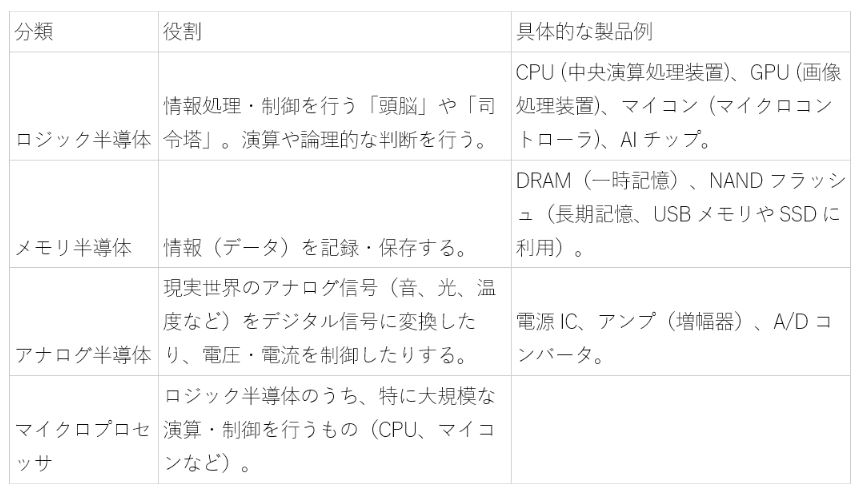

1-1. 用途・機能による主な分類(半導体製品)

半導体デバイスは、大きく分けて集積回路(IC)と個別半導体素子(ディスクリート)に分類されます。

1-1-1. 集積回路(IC: Integrated Circuit)

複数のトランジスタ (transistor) やダイオード (diode) 、抵抗 (resistor) などを一つのシリコンチップ上に集積し、複雑な機能を実現したものです。現代のエレクトロニクスの主役と言えます。以下は、その分類表です。

1-1-2. 個別半導体素子(ディスクリート)

単一の機能を持つ、集積度の低い素子です。その分類表を以下に示します。

1-2. 材料による分類(次世代半導体を含む)

1-2-1. シリコン系半導体(Si)

最も一般的で、長年にわたり半導体産業の主流材料です。安価で安定しており、大規模な集積回路(IC)に広く使われています。

1-2-2. 化合物半導体 (compound semiconductor)

2種類以上の元素からなる半導体で、Siには無い優れた特性を持ちます。

- SiC(Silicon Carbide: 炭化ケイ素)

- 特徴:バンドギャップ(bandgap)がSiより大きく、高耐圧 (high-voltage)、高耐熱(high thermostability)、低損失(low-loss: 電力損失が少ない)

- 用途:パワー半導体(電気自動車のインバータ:inverter、新幹線、産業機器)の分野で急速に採用が拡大しています。

- GaN(窒化ガリウム:Gallium Nitride)

- 特徴:高速動作が可能で、電力効率が高い

- 用途:パワー半導体(特に低~中電圧域)、高周波通信(5G基地局)、LED(blue LED: 青色発光ダイオード の材料)

- GaAs (ガリウムひ素 または ヒ化ガリウム)

- 特徴:高速動作、光との相性が良い

- 用途:光通信、スマートフォンなどの高周波回路(RFデバイス)

2.半導体メーカの開発方式(垂直統合と水平分業)

半導体の開発方式には、大きく分けて垂直統合型(IDM)と水平分業型の2つがあります。我が国では過去に垂直統合型で複数社が個別に設備投資を行った結果、資金力のある海外のメーカの後塵を拝する結果となりました。現在でも我が国が強みを持ついくつかの特別な製品については、垂直統合型の開発形態がとられているようです。しかしながら、近年では我が国の半導体メーカも国際化が進み、国内外の協力会社を利用した水平分業が行われることが増えてきています。

2-1. 垂直統合型(IDM): 自社で全てを

垂直統合型(Integrated Device Manufacturer: IDM)は、半導体の設計、製造(前工程・後工程)、そして販売まで、すべての工程を一貫して自社で行う方式です。

特徴

- 強み: 全工程を自社で管理できるため、技術の機密保持が容易で、設計と製造の連携を密にして高性能な製品を開発しやすいです。また、市場の変化に素早く対応し、生産計画を柔軟に調整できます。

- 弱み: 自社の工場(ファブ)に莫大な設備投資が必要となり、固定費が高くなります。市場の需要が落ち込んだ際のリスクも大きくなります。

具体的な例

- Intel(インテル): 長らく、パソコンの頭脳であるCPU(中央演算処理装置)を自社で設計し、自社の工場で製造するIDMの代表格でした。これにより、高性能なCPUを市場に提供し続けてきました。

- Samsung Electronics(サムスン電子): メモリ半導体(DRAMなど)やロジック半導体において、設計から製造までを一貫して行う世界的なIDMです。

- Texas Instruments(テキサス・インスツルメンツ): アナログ半導体などの分野で設計・製造を自社で行っています。

2-2. 水平分業型: 専門性を活かす

水平分業型(horizontal specialization, or fabless-foundry model)は、半導体の開発プロセスを設計、製造、そしてテスト・パッケージングといった専門分野ごとに異なる企業が分担する方式です。

特徴

- 強み: 各企業がそれぞれの専門分野に集中することで、高度な技術革新が進みやすくなります。設計企業は製造設備への投資が不要となり、低コストで製品開発が行え、参入障壁が下がります。

- 弱み: 設計情報や機密技術が分担先へ流出するリスクがあります。また、異なる企業間の調整が必要となるため、IDMほど密接な連携が取りにくい場合があります。

具体的な例(構成要素)

水平分業型は、主に以下の3種類の企業で構成されています。

- (A)ファブレス(Fabless):設計に特化し、自社工場を持たない企業です。

例: NVIDIA(エヌビディア)(GPU : Graphical Processing Unit)、Qualcomm(クアルコム)(スマートフォン向けSoC : System on Chip)、MediaTek(メディアテック)など。 - (B)ファウンドリ(Foundry):製造に特化し、ファブレス企業などから委託を受けて半導体ウェハプロセス(前工程)を行う企業です。

例: TSMC(台湾積体電路製造)(世界最大手)、Samsung Foundry(サムスン電子のファウンドリ部門)など。 - (C)OSAT(Outsourced Semiconductor Assembly and Test): 後工程(組み立て、テスト、パッケージング)を専門に行う企業です。

例: ASE Technology Holding、Amkor Technologyなど。

現代の半導体業界は、特にロジック半導体において、この水平分業型が主流となりつつあります。設計に特化したNVIDIAなどが、製造に特化したTSMCに生産を委託することで、高性能な製品を効率的に開発・供給しています。

3.半導体の基本原理

PN接合は、現代の電子機器の基盤となる非常に重要な技術です。シリコン(Si)を例にとって、その基本原理から応用デバイスの動作までを順を追って説明します。

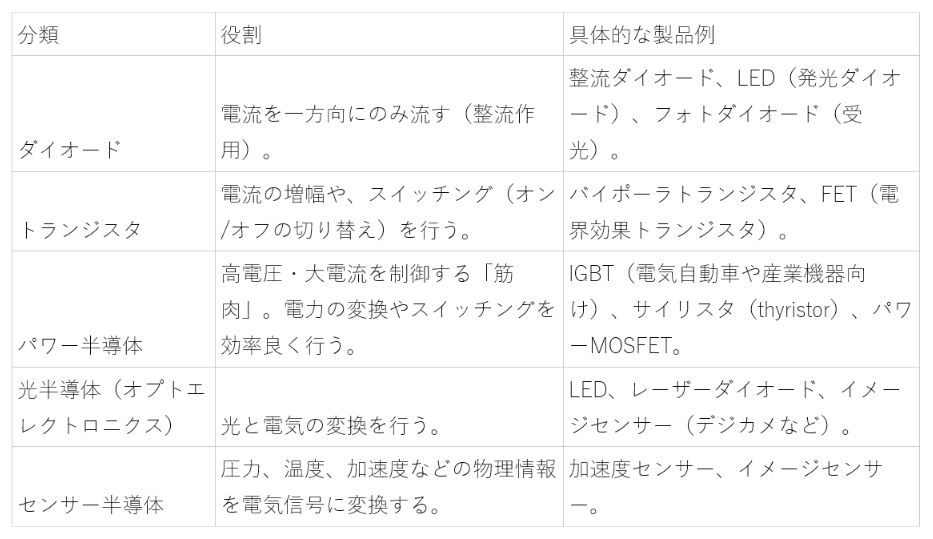

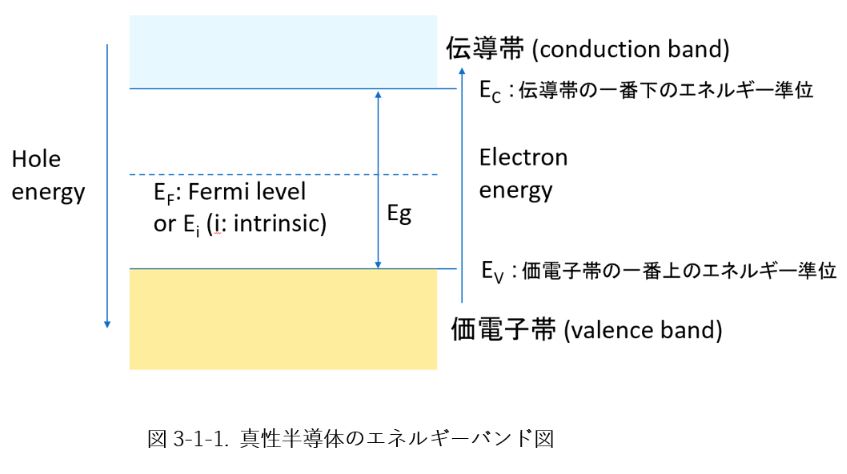

3-1. 結晶のバンド理論

半導体の電気的性質を理解するための基本がバンド理論(Band theory)です。結晶体の中の電子の取り得るエネルギー(エネルギー準位という)を量子力学的に解析すると、帯状に分布することが分かっているため、バンド理論と呼ばれます。

- 価電子帯(Valence Band: VB): 原子核に強く束縛された電子(価電子)が満たしているエネルギー帯です。通常、電子で満たされている状態で自由に移動できる電子が無いため、電流を流しません。

- 伝導帯(Conduction Band: CB): 外部からエネルギーを与えられた電子が飛び移る、空のエネルギー帯です。伝導帯に入った電子は結晶内を自由に移動でき、電流を流すことができます(自由電子)。

- バンドギャップ(Band Gap: Eg): 価電子帯と伝導帯の間にある、電子が存在できないエネルギーの領域です。またの名前を禁制帯といいます。また、バンドギャップの大きさ(禁制帯幅)を表す単位としては、通常電子ボルト(eV)が用いられます。これは、電子1個が電圧1Vで加速されるときに得るエネルギーに相当します。

シリコン(Si)のような半導体では、バンドギャップは比較的狭い(Siでは約1.12 eV)ため、熱エネルギーなどで一部の電子が価電子帯から伝導帯へ容易に励起されます。この励起によって自由電子と、価電子帯に残された電子の抜け穴である正孔(hole : ホール)が発生し、これが電気伝導を担います。

下図2-1-1は、真性 (intrinsic) 半導体を例に、価電子帯、導電帯、禁制帯を簡易的に図で表したものです。このような図は、エネルギーバンド図と呼ばれます。図で上に上がるほど電子のエネルギーは大きくなり、下に行くほど正孔のエネルギーが大きくなります。電子、正孔ともに、自然のかたちではエネルギーの大きい準位からエネルギーを放出してエネルギーの小さい準位(空きがあれば)に遷移しようとします。中央にあるフェルミレベルとは、量子力学で電子の存在確率が1/2になるエネルギー準位です。

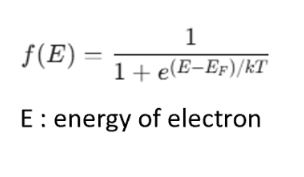

なお、フェルミ・ディラック統計(統計物理学)によると、電子が特性のエネルギー準位を占有する確率は、次のようになります。f(E) を、フェルミ・ディラックの分布関数と呼びます。ここで、Eは電子のエネルギーを示します。

E=EFの時、分母は2になり、電子の存在確率が1/2 となります。

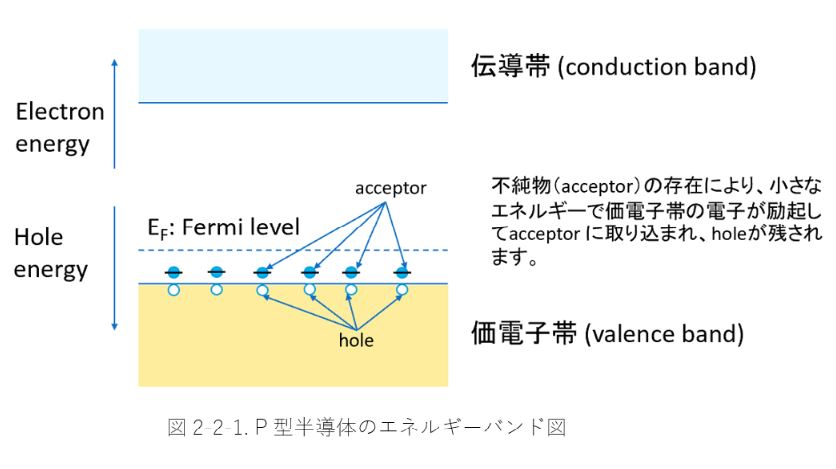

3-2. P型半導体

真性半導体(intrinsic Silicon : 純粋なSi)に、III族の元素(最外郭に3個の価電子を持つ(例: ホウ素(B: Boron)やインジウム(In: Indium))を微量添加(doping : ドーピング)して作られます。

- ドーピングの仕組み: Si原子は4つの価電子を持つのに対し、B原子は3つの価電子しか持ちません。B原子がSi結晶に取り込まれると、隣接するSi原子との結合を完成させるために電子が不足します。

- キャリア (carrier) : この不足した電子の場所が正孔(ホール)として機能します。正孔は正の電荷を持つキャリアとして振る舞い、結晶内を移動できます。

- 多数キャリア (majority carrier) : 正孔。

- 不純物 (dopant) : アクセプター(acceptor: 電子を受け取るという意味)。

図2-2-1にP型半導体のエネルギーバンド図を模式的に示します。フェルミ準位が価電子帯に近くなっているのが分かります。また、アクセプターは、価電子帯のすぐ上のエネルギー準位に存在しています。

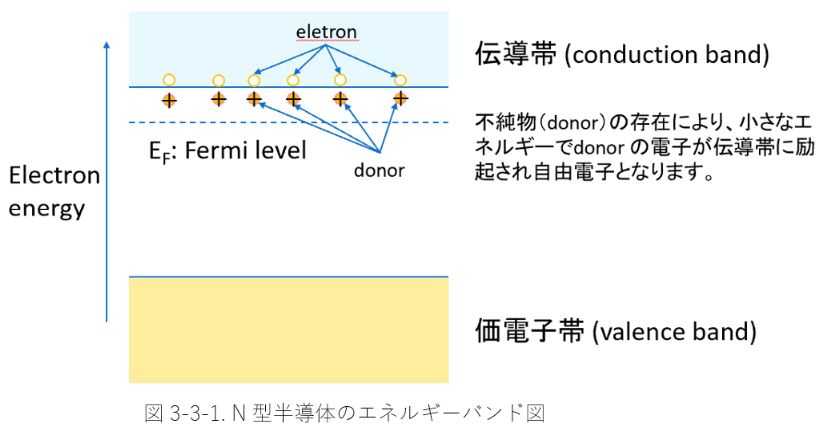

3-3. N型半導体

真性半導体(intrinsic Silicon : 純粋なSi)に、V族の元素(最外郭に5個の価電子を持つ元素、例: リン(P: Phosphorous)やひ素(As: Arsenide))を微量添加(doping : ドーピング)して作られます。

- ドーピングの仕組み: P原子は5つの価電子を持つのに対し、Si原子は4つの価電子しか持ちません。P原子がSi結晶に取り込まれると、隣接するSi原子との結合に使われずに余った電子が1つ生じます。

- キャリア: この余った電子はわずかなエネルギーで結晶内を自由に動き回る自由電子 (free electron) になります。

- 多数キャリア (majority carrier) : 電子 (electron)。

- 不純物 (dopant) : ドナー(donor : 電子を提供するという意味)。

N型半導体のエネルギーバンド図を模式的に次に示します。フェルミ準位は、伝導帯に近くなっています。なお、ドナーは伝導体に近いエネルギー準位に分布します。

3-4. フェルミレベル(Fermi Level: EF)

フェルミレベルは、電子が存在する確率がちょうど50%となるエネルギー準位を示す指標です。

- 真性半導体: バンドギャップの中央付近に位置します(Eiとも表示される)。

- P型半導体: 正孔が多数キャリアなので、電子が少ない状態を示し、フェルミレベルは価電子帯に近づきます。

- N型半導体: 電子が多数キャリアなので、電子が多い状態を示し、フェルミレベルは伝導帯に近づきます。

3-5. PN接合とその動作

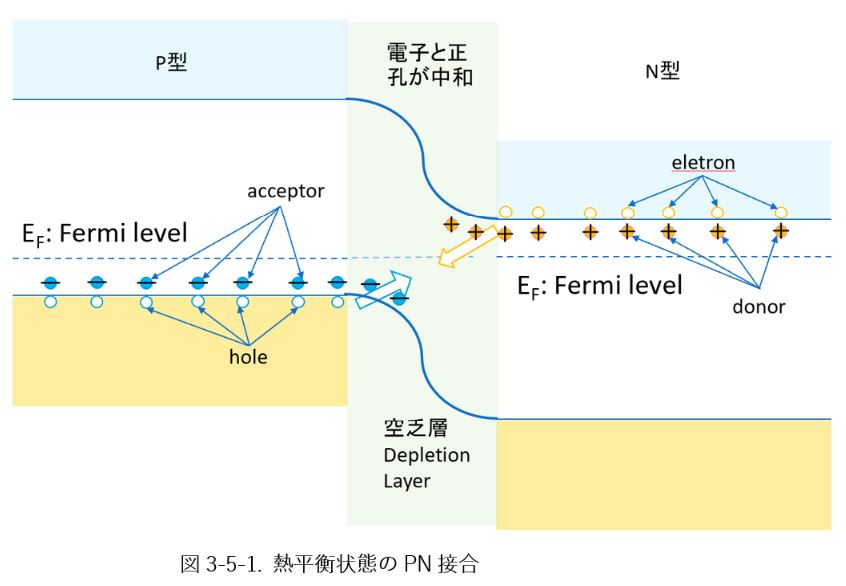

P型半導体とN型半導体を一つの結晶内で接合したものがPN接合です。

3-5-1. 平衡状態(バイアスなし)

- 拡散: 接合直後、N側の多数キャリア(電子)がP側へ、P側の多数キャリア(正孔)がN側へ移動(拡散)し、互いに再結合して消滅します。

- 空乏層(Depletion Layer)の形成: キャリアが再結合により失われた接合部付近には、動きを封じられた不純物イオン(N側: 正のドナーイオン、P側: 負のアクセプターイオン)のみが残り、キャリアが存在しない領域ができます。これを空乏層と呼びます。

- 内部電界と電位障壁: 空乏層内のイオンが作る電界(N側からP側へ)は、それ以上のキャリアの拡散を妨げる電位障壁(Built-in Potential)となります。

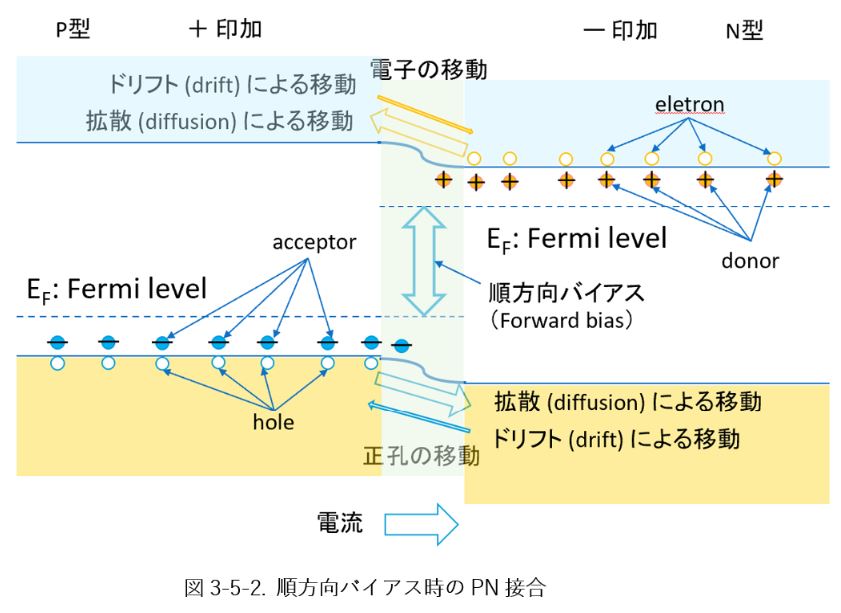

3-5-2. 順方向バイアス(Forward Bias)

- 印加電圧: P側に正、N側に負の電圧を加えます。

- 動作: 外部電圧が内部電界を打ち消すように働き、電位障壁が低くなります。これにより、N側の電子とP側の正孔が空乏層を越えて相手の領域に流れ込みやすくなり(キャリア注入: carrier injection)、再結合 (recombination)しながら電流が流れます。電位障壁を超えて相手の領域に流れ込むのは、多数キャリアの拡散 (diffusion) に依るもので、電位差(電界)により逆方向にも少数キャリアのドリフト (drift)による微量の流れ込みがあります。

- 特性: ある電圧(VF、Siでは約0.7 V)を超えると、電流が指数関数的に増加します。これも、量子力学を使ったフェルミ・ディラックの統計物理学によります。

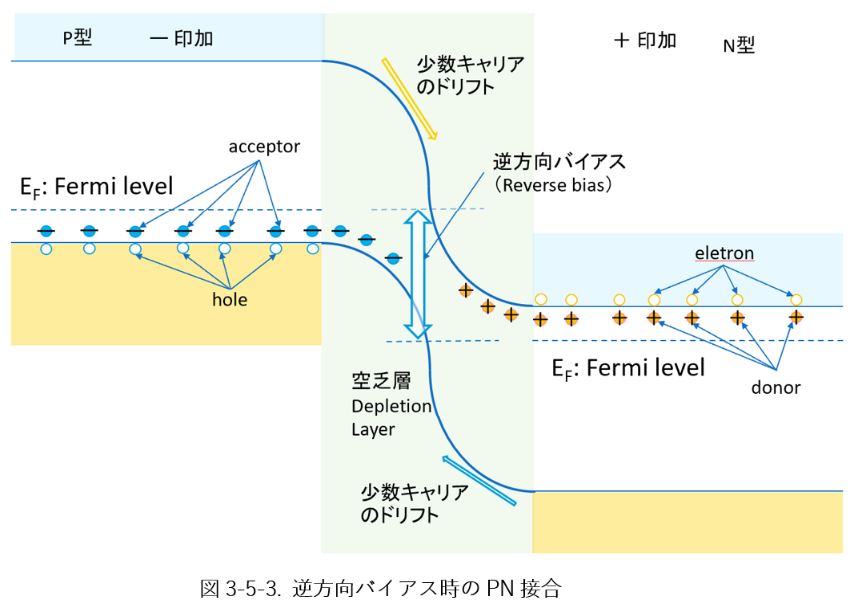

3-5-3. 逆方向バイアス(Reverse Bias)

- 印加電圧: P側に負、N側に正の電圧を加えます。

- 動作: 外部電圧が内部電界を強めるように働き、電位障壁がさらに高くなります。多数キャリアは接合部から遠ざけられ、空乏層が広がります。

- 特性: 多数キャリア (majority carrier) による電流はほとんど流れません。ごくわずかな逆方向飽和電流(電界による少数キャリア: minority carrierのドリフト: drift 電流)が流れるのみで、電流はほぼゼロとなります。ただし、電圧を上げすぎると降伏(ブレークダウン: breakdown)を起こし、急激に大電流が流れます。ひどいときには、デバイスが過熱して破壊することもあるので、注意が必要です。

3-6. PN接合と半導体デバイス

3-6-1. PN接合ダイオード

PN接合は、電流を一方向にしか流さないという整流作用を持つ電子部品(ダイオード)として利用されます。

3-6-2. バイポーラ接合トランジスタ

バイポーラ接合トランジスタ(Bipolar Junction Transistor: BJT)は、PN接合を2つ背中合わせに配置した構造(NPN型またはPNP型)により、増幅作用とスイッチング作用を持つ素子です。

3-6-3. サイリスタ

サイリスタ(Thyristor)は、PN接合を3つ直列に接続した4層構造(PNPN)を持つ素子で、主に電力制御に使われる自己保持型(ラッチング: latching)スイッチです。

【補足】なお、1947年にBardeenとShockley が発見した点接触型トランジスタは、金属と半導体の接合部にできるショットキー障壁 (Schottky barrier) により、PN接合と同じような整流作用があることを利用したものです。

無断転載・無断使用を禁じます。