Table of Contents

半導体とその微細化の進展

1.半導体とは?

最近、色々な媒体で半導体の情報を目にする機会が増えてきました。半導体は、我々の社会に不可欠な技術として、今後益々ニーズが高まると予想されています。

ところで半導体(semiconductor)とはどのような物質のことでしょうか?物質には導体(conductor)と絶縁体(insulator)があります。導体は電気を通すもので、例えば金、銀、銅、アルミなどの金属は導体に分類されます。一方、空気、ガラス、ゴム、陶器などは絶縁体に分類されます。半導体は導体と絶縁体の中間の特性を持ち、条件によって導体にも絶縁体にもなる物質です。その特性により電気のON/OFFを制御することが可能で、シリコン(Si)やゲルマニウム(Ge)などが代表的な半導体として知られています。

これらは元素そのものですが、化合物半導体として知られるものもあり、例を挙げるとガリウムひ素(GaAs)や炭化シリコン(SiC)、窒化ガリウム(GaN)などがあります。

2.半導体素子の誕生

初めて半導体の素子の動作が確認されたのは、1947年12月のことで、場所はアメリカのベル研究所(Bell Laboratory)でした。John BardeenとWalter Brattainという2人の科学者によるものです。

使われたのはゲルマニウムの単結晶で、その上に2本の細い金属の針を点接触させゲルマニウムの裏側にも電極を付けた構成でした。一方の針がエミッタ(Emitter)、もうひとつの針がコレクタ(Collector)、裏側の電極はベース (Base) とされ、エミッタから電子が注入され、コレクタから電子を受け取ります。このとき、エミッタから注入される信号に対して、コレクタ側では大きな出力信号が得られ、信号の増幅作用が確認されました。これを点接触型トランジスタ (pin-contact transistor) といいます。

Bardeen と Brattain に加えて、この研究を指導したWilliam Shockleyの3人は、1956年にノーベル物理学賞を受賞しました。しかしながら、点接触では量産性に課題があり、その後Shockleyが提案した接合型トランジスタ(junction transistor)が主流になります。

ここで発明されたのは、バイポーラトランジスタ(bipolar transistor)と呼ばれる素子です。半導体素子としては、このようなトランジスタ(transistor)、ダイオード (diode) 、サイリスタ(thyristor)などのディスクリート(discrete)素子などが作られ、やがてそのような素子をひとつの半導体基板上に集積し、配線を施すことで単一の電子回路として機能する集積回路(IC, Integrated Circuit)が発明されました。

この発明には、当時TI(Texas Instruments)の技術者であり、Kilby特許で有名なJack KilbyとFairchild Semiconductorを共同創業したRobert Noyce(Intelの創業メンバのひとりでもある)が関わっています。集積化が進むにつれ、ICに組み込まれる素子としては、電解効果型トランジスタ(FET, Field Effect Transistor)、中でも低消費電力で優位なCMOS(Complementary Metal Oxide Semiconductor)タイプのFETが主流となっていきます。そのような流れの中で、我が国でも特に半導体メモリ(memory)の技術開発が進みました。

3.日本半導体メーカの全盛期:1980年代

1980年代は日本の半導体メーカにとっての全盛期でした。特にDRAM(Dynamic Random Access Memory)において、日本は世界のリーダーでした。NEC、東芝、日立、三菱電機、富士通などが、当時の半導体市場を席巻したのです。この当時、半導体メーカは自社内で設計、製造、そして最終製品までを一貫して手掛ける垂直統合型のビジネスモデルを採用していました。

この全盛期の鍵を握っていたのが、微細化技術です。この時期、半導体のプロセスノード(process node) は数ミクロンから1ミクロン台へと急速に進化しました。例えば1980年代初頭には3umプロセスが主流でしたが、1980年代後半には1umプロセスが実用化されました。これにより、1つのチップに集積できるトランジスタの数が増大し、性能向上とコスト削減が同時に進みました。日本のメーカは、高品質で信頼性の高い製品を大量生産する能力に優れていました。これは日本の高度な製造技術と、徹底した品質管理に支えられたためです。

このような日本メーカの台頭に危機感を強めていったのが、アメリカの半導体メーカです。そして、アメリカの半導体工業会(SIA)は、日本のDRAMとEPROM(Erasable Programmable Read-Ony Memory)が不当に安く輸出されているとして、アメリカ政府にダンピング調査を求め、これを受けて日米両政府間で協議が行われ、1986年9月に「日米半導体協定」が締結されました。この協定には主に、ダンピングの防止と日本市場における外国製半導体のシェア改善の2つの内容が盛り込まれました。これらにより、日本のメーカの価格競争力の著しい低下と、外国製半導体の購入の事実上の圧力をまねきました。

4.日本メーカの後退と韓国、台湾メーカの台頭

1990年代に入ると、日本の半導体産業は徐々にその輝きを失い始めます。いくつかの要因が複合的に絡み合っていました。

まず、DRAMの価格競争の激化です。韓国のサムスン電子やLGエレクトロニクスが、大規模な設備投資と効率的な生産体制を武器に、低価格攻勢を仕掛けてきました。日本のメーカは、高コスト体質から抜け出せず、価格競争で劣勢に立たされました。

次に、ファブレスとファウンドリの台頭です。ファブレスは自社で製造設備を持たず、半導体の設計に特化するビジネスモデルです。一方、ファウンドリは他社の半導体を製造する受託生産に特化するビジネスモデルです。これらの新しいビジネスモデルが世界的に広まる中、日本の多くのメーカは依然として垂直統合モデルに固執し続けました。これにより、迅速な技術革新や市場の変化への対応が遅れ、競争力を失っていきました。

微細化技術においても、日本のメーカは徐々に遅れを取り始めます。1990年代中盤には0.35μm、後半には0.18μmプロセスが主流となりました。当時、半導体製造工場の微細化のための投資額は一社では賄えない大きさになっていました。日本の各社は個別に投資を続けたため、研究開発費が分散し、そのため効率的な微細化競争ができなくなったのです。

2000年代に入ると、台湾と韓国のメーカが半導体業界の主役に躍り出ます。

台湾のTSMC(Taiwan Semiconductor Manufacturing Company)は、世界最大のファウンドリとして、ファブレスメーカからの製造受託を拡大し、急成長を遂げました。TSMCは、最先端の製造プロセスに莫大な投資を行い、微細化競争の最前線を走るようになりました。2000年代には90nm、65nm、45nmといったプロセスノードを次々と実用化し、半導体製造のグローバルスタンダードを確立しました。

一方、韓国のサムスン電子は、DRAMとNANDフラッシュメモリの分野で圧倒的なシェアを確保しました。サムスンは、DRAM市場の価格競争で日本企業を駆逐した後、NANDフラッシュメモリ市場でも同様の戦略を取り、市場を独占しました。サムスンは、設計から製造までを一貫して手掛ける垂直統合モデルを維持しつつも、大規模な投資を継続することで、微細化技術でも常にトップグループを走り続けました。

台湾、韓国などでは、政府による半導体産業へのテコ入れが行われ、大規模な投資に対するリスクを軽減する政策がとられていました。一方で、日本の半導体メーカは、事業売却や統合を余儀なくされました。やがて、NECと日立のDRAM事業が統合されエルピーダメモリが設立されたり、東芝のメモリ事業が独立したりするなど、再編が進みました。

5.スマートフォンと半導体

2007年の初代iPhoneの登場以来、スマートフォンは半導体市場の最大の牽引役となりました。スマートフォンには、CPU、メモリ、センサー、無線通信チップなど、さまざまな種類の半導体が搭載されています。特に、モバイルプロセッサの性能向上には、微細化技術が不可欠でした。

6. AIの時代と半導体

現代は、AI(人工知能)の時代に突入しました。AIの演算には、膨大な量のデータを高速に処理する能力が求められます。この要求に応えるため、AI半導体、特にGPU(Graphics Processing Unit)やAIアクセラレータの需要が急増しました。

AI半導体の性能を向上させるためには、さらなる微細化が不可欠です。現在、最先端のプロセスノードは、7nm、5nm、そして3nmへと進化しています。これにより、1つのチップに数十億から数百億ものトランジスタを集積できるようになりました。

この微細化競争は、技術的な難易度が極めて高くなっています。EUV(Extreme Ultraviolet)露光装置のような、莫大な投資と高度な技術を必要とする装置が不可欠となりました。現在、このEUV装置を製造できるのは、オランダのASML社のみです。このような状況が、半導体製造の寡占化をさらに加速させています。

日本は、この最先端の製造プロセス競争からは一歩後退しましたが、半導体製造装置や材料の分野では、依然として高い競争力を維持しています。例えば、東京エレクトロン、スクリーンホールディングス、アドバンテストといった企業は、世界市場で大きなシェアを占めています。

7.今後の展望

今後の半導体産業は、AI、IoT(Internet of Things)、自動運転、量子コンピュータといった新しい技術領域に支えられ、さらなる成長が期待されます。

微細化は、物理的な限界に近づきつつあります。そのため、今後は単にプロセスノードを縮小するだけでなく、3D積層技術(複数のチップを垂直に積み重ねる技術)や、ヘテロジニアス・インテグレーション(異なる機能を持つチップレットを統合する技術)といった新しいアプローチが重要になってくるでしょう。これにより、性能向上と消費電力削減の両立を目指します。

日本は、最先端のプロセスノードでの製造は現時点では困難ですが、半導体製造装置や材料、そして特定の用途に特化したパワー半導体やイメージセンサーといった分野で、再び存在感を示す可能性があります。

例えば、新しいプロセスノードの開発を目指すRapidusの動向が注目されています。これは、日本政府と複数の大手企業が協力して設立された、次世代半導体の国産化を目指すプロジェクトです。

日本の半導体産業は、1980年代の成功から衰退に転じる体験の中で、多くの教訓を得ました。これからの時代は、過去の垂直統合モデルに固執するのではなく、得意な分野に特化し、世界中のパートナーと協力することで、新しい価値を創造していくことが重要となるでしょう。

補足資料(微細化とデバイス構造の例)

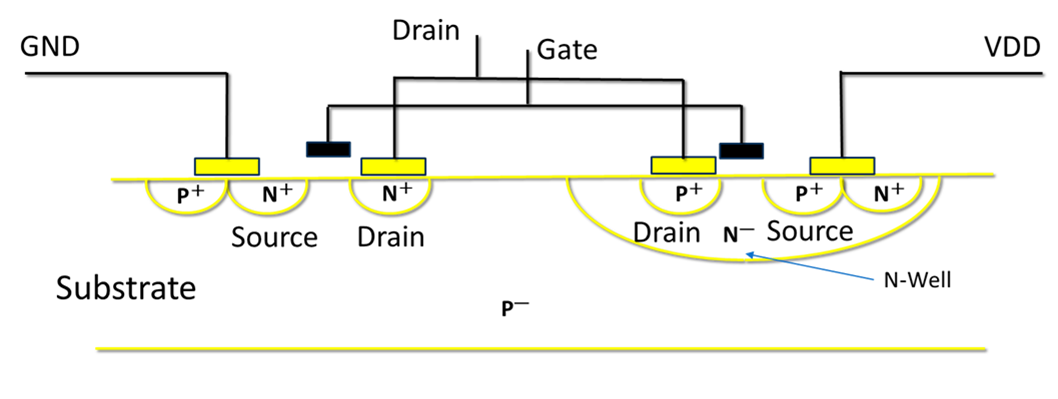

プレーナ型CMOS構造

Planer Complementary Metal Oxide Semiconductor

これは、シリコン基板上の素子と配線の断面図の一例です。プレーナ型というのは、平面上に作りこまれた素子構造をいいます。トランジスタ(Field Effect Transistor)は、ソース(Source)、ゲート(Gate)、ドレイン(Drain)から構成されています。図でP, Nの右上の+、(ー)は、それぞれ不純物のdoping濃度のより高い(低い)P型、N型を表します。濃度が高いほど抵抗は小さくなります。P型、N型は、それぞれ電流を運ぶCarrierが主に正孔 (hole)、電子 (electron)であり、不純物を添加されたものです。P型、N型については、次号で詳しく説明します。

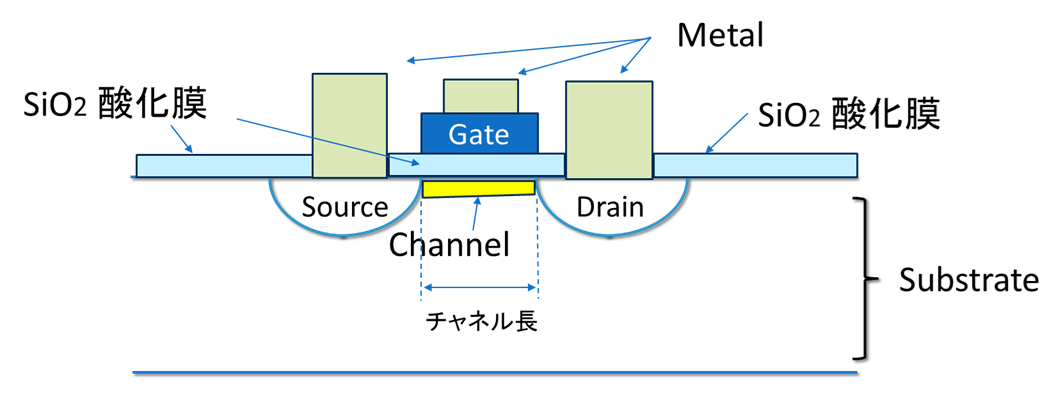

上記は、FET(Field Effect Transistor:電解効果トランジスタの部分に注目した断面図の例です。電気を導通するのは、Metal、Gate、Source、Drainで、絶縁体は酸化膜SiO2です。Channelの部分はGateに与えられるバイアス電圧により、ON/OFFされます。このように、プレーナ型ではGateの下にあるチャネルのみがトランジスタの導通に関与します。

数ミクロンからサブミクロン(~0.1um)のプロセスノードでは、このようなシリコン基板の表面に回路を集積化するのが主流でした。ところが近年微細化がさらに進んで、数十ナノメータのプロセスが使われるようになると、プレーナ型ではチャネル長が小さく(ソース、ドレイン間の距離が近く)なり過ぎて、いわゆる短チャネル効果(short-channel effect)などにより正常なトランジスタの動作が保証できなくなってきました。

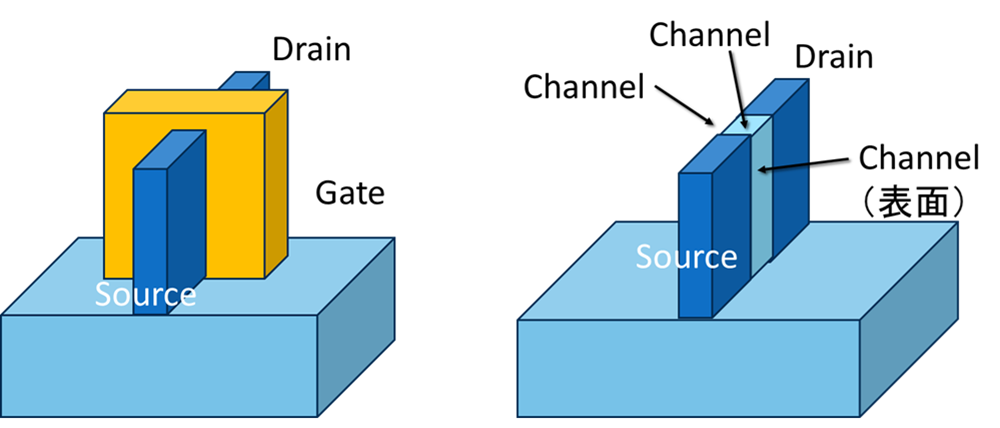

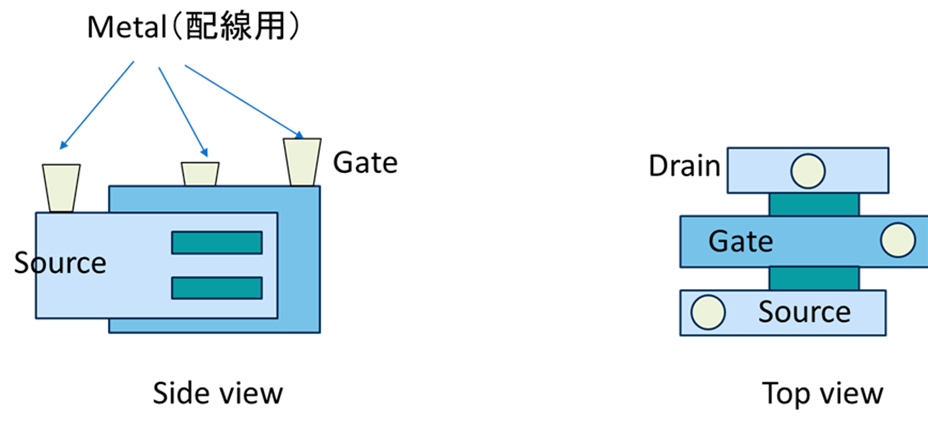

そこで考案されたのが、次のFin FETという構造です。チャネルが右、上、左の3つの面で形成されるため、ある程度チャネル長を確保しても十分な駆動を行えるのが特長です。製造プロセスは、プレーナ型に比べてかなり複雑になります。

さらなる微細化(<10ナノメータ)の進展に対応するため考案されたのが、次のGAA(Gate All Around)構造です。この構成では、チャネルがソース・ドレイン間で上下左右の4つの面に対して形成されるのが特長です。図は、そのようなFETを2個並列に作りこんだ例です。製造工程は、さらに複雑になります。

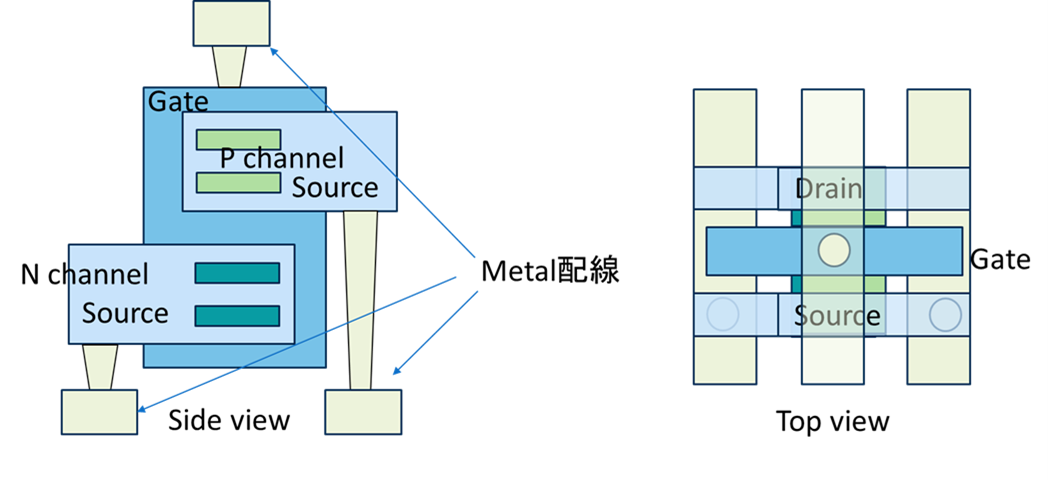

最後にご紹介するのは、CFETと呼ばれる近未来の構造です。GAAの構造をPチャネル、Nチャネルそれぞれのトランジスタに適用し、さらにこれらを3次元状に積み上げることで、素子の面積を極力小さくしながらCMOS構造を実現するものです。現在開発が進んでいる数ナノメータから1ナノメータのプロセスノードで検討されています。

無断転載・無断使用を禁じます。