Table of Contents

第4回 半導体プロセス詳細解説(1)

1.半導体プロセスの概要

1-1. Siから半導体デバイスになるまで

半導体デバイスに使われるシリコンは、極めて高純度 (99.9999999%) のものです。また、結晶欠陥に対しても同様に厳しい要求レベルがあります。そのため半導体デバイスに要求される水準を満たすシリコンウェハを供給できるメーカーは限られています。そのような中で、我が国には世界第1位、2位のシェアを持つ信越化学工業とSUMCOがあり、この2社で世界シェアの半分以上を占めています。

1-1-1. 洗浄

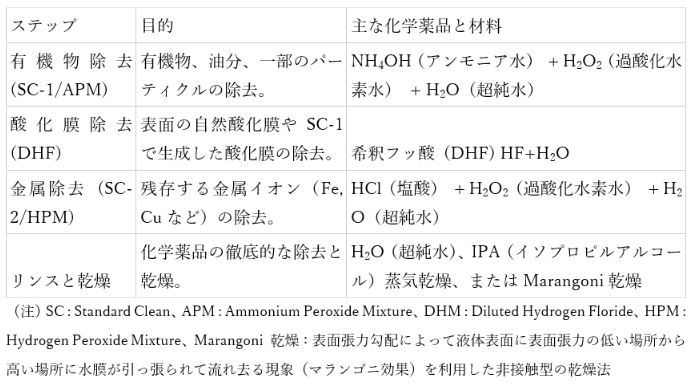

シリコンウェハ上に微細な素子や配線を張り巡らして集積回路(IC)にするまでの工程を前工程といいます。前工程の最初にウェハ洗浄が行われます。これは、イニシャルクリーニングと呼ばれ、RCA(Radio Corporation of America)で開発された洗浄の派生技術をベースにした多段階の工程からなる洗浄法です。目的は、ウェハ表面に付着した汚染物質を次の工程に進む前に除去することです。代表的な汚染物質は、次の通りです。

- (A)パーティクル(微粒 : particle):大気中の埃や製造装置から発生する微粒子

- (B)有機汚染:ワックス、オイルなど

- (C)金属汚染:Fe(鉄)、Cu(銅)、Na(ナトリウム)などの金属イオン

洗浄は、次の主要なステップを組み合わせて行われます。

1-1-2. イオン注入

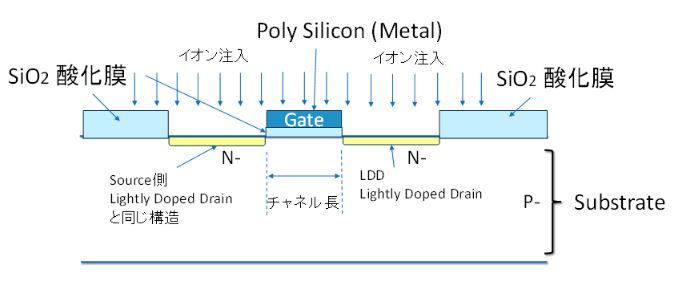

現在主流の半導体集積回路は、ウェハ上にMOSFET (Metal Oxide Semiconductor Field Effect Transistor) というトランジスタ素子を集積化しています。このトランジスタは、ソース、およびドレインと呼ばれる領域の間(下図中央)にゲート領域を持ち、上からMOS(金属、酸化膜、半導体)が重なっています。ソース、ドレインにはイオン注入により導電性を持たせています。下の例は、基板(Substrate)がP型で、ソース、ドレインがN型 (N-channel MOSFET) の場合です。

- (A)LDD構造の形成(Lightly Doped Drain:低濃度注入)

微細化が進んだトランジスタでは、チャネル長が短いためにゲート端付近で電界が集中する短チャネル効果(short channel effect)を抑制するため、LDD構造と呼ばれる低濃度のソース、ドレイン領域を形成します。N型MOSFETの場合、ソース、ドレインにはAs(ヒ素)またはP(リン)のイオンが打ち込まれます。

シリコン基板の酸化膜やゲートをエッチングして取り除いた領域に、低濃度で低いエネルギーのイオン注入が行われます。酸化膜やゲートは、イオンの透過を阻止するマスクとなります。

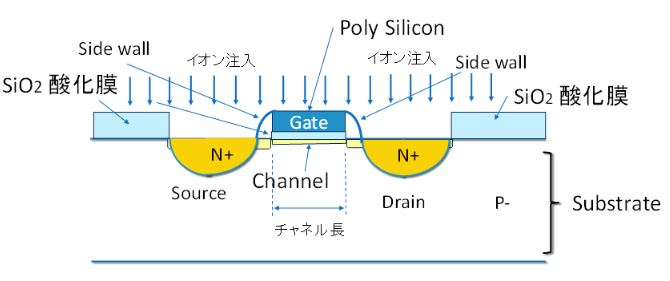

- (B)サイドウオール(side wall)の形成

まず、SiO2やSiNなどの絶縁膜をウェハ全体に均一に堆積させます。次に堆積した絶縁膜を異方性エッチングにより垂直方向に除去し、ゲート電極の側壁部分に絶縁膜を残します。

- (C)ソース、ドレイン本体の形成(高濃度イオン注入)

側壁(side wall)をマスクとして利用し、高濃度で中~高エネルギーの不純物イオンを注入することで、FETのソース(Source)、ドレイン (Drain) 領域を形成します。ゲート(Gate)にプラス電圧を印加すると、酸化膜を介して電解が半導体基板に及び、酸化膜の直下に電子のチャネルが誘起され、FETトランジスタがON状態になります。

- (D)アニーリング(annealing、アニール処理)

イオン注入によりウェハの結晶構造に損傷が生じているため、また注入した不純物を電気的に活性化するため、必ずアニーリング(活性化熱処理)を行います。これにより結晶欠陥の修復と、注入された不純物原子を結晶格子中の置換位置への移動を行うことで、電気的にキャリアを放出できるようにするものです。

1-1-3. ゲート電極の形成

- (A)ゲート絶縁膜の成膜

まず、ウェハ表面のチャネル領域となるシリコンの上に、極めて薄い絶縁膜を形成します。

従来は、熱酸化により極めて質の高い二酸化ケイ素 (SiO2) 膜を形成していました。微細化が進んだ現在では、ゲートリークを抑えるため、比誘電率の高い(High-k : High dielectric constant)材料(ハフニウム酸化物:HfO2など)をALD(Atomic Layer Deposition : 原子層堆積)法などの精密な成膜技術で形成します。

- (B)ゲート電極材料の成膜

ゲート絶縁膜の上に電極となる導電性材料を成膜します。従来はポリシリコン(多結晶シリコン)をCVD(Chemical Vapor Deposition : 化学気相成長)法で堆積していました。現在ではアルミニウム、タングステン、チタンナイトライド(TiN)などの金属材料をPVD(Physical Vapor Deposition)やALD(Atomic Layer Deposition)などの技術で成膜します。

- (C)パターニングとエッチング

成膜されたゲート電極材料を、設計された通りの形に加工します。

- リソグラフィ: ゲート電極材料の上にフォトレジストを塗布し、フォトマスクと露光装置(ステッパーなど)を使ってゲートの幅と長さに対応した回路パターンを転写します。

- エッチング: レジストをマスクとして、ドライエッチング(反応性イオンエッチング: RIE Reactive Ion Etching)により、ゲート電極材料を異方性(垂直方向)に深く掘り込みます。

- レジスト除去: パターニングが終わった後、残ったフォトレジストを剥離(アッシング : ashing)します。

このエッチング工程により、細長い線状のゲート電極が形成され、これが1-1-2で説明したソース/ドレインへのイオン注入時にマスクとして働きます。

1-1-4. 配線

次に配線について説明します。トランジスタ(FET)が形成されると、そのゲート、ソース、ドレインの配線が金属を用いて行われます。

- (A)コンタクトの形成

コンタクトは、トランジスタのSi領域(ソース、ドレイン)と上層の金属配線層を電気的に接続するビアホール(via hole)のような垂直な穴です。

Step1:シリサイド化

トランジスタの動作速度と電力効率向上のため、ソース、ドレインのSi表面の抵抗値を

下げる工程がよく使われます。

- 金属膜の成膜:ニッケル(Ni)やコバルト(Co)などの金属をSi表面に堆積させます。

- アニーリング(熱処理):熱を加えることで、金属とSiが反応し、金属シリサイド(NiSi Nickel Silicide, CoSi Cobalt Silicide)と呼ばれる低抵抗の化合物層が形成されます。この工程は、サリサイド(Self-aligned Silicide)法とも呼ばれます。

Step2:層間絶縁膜 (ILD) の成膜とコンタクトホールの形成

- ILDの形成:ゲート電極とシリサイド層の上に、最初の層間絶縁膜ILD (Inter Layer Dielectrics)、主にSiOやLow-k : Low dielectric constant膜)を堆積させます。

- 平坦化:CMP(化学機械研磨)で膜表面を平坦にします。

- パターニング:リソグラフィとエッチングにより、ソースとドレインの金属シリサイド層に到達するコンタクトホール(穴)を開けます。

Step3: コンタクトホールの埋め込み

- バリア (barrier) 層成膜:Siと上層の金属が反応しないように、コンタクトホール内にバリアメタル(barrier metal、例:TiやTiN)を成膜します。

- タングステン(W)埋め込み:ホール内にWをCVD法で堆積させ、穴を完全に埋め込みます。Wはコンタクト材として優れた特性(Siとの反応性が低い、高い融点など)を持っています。

- CMP:余分なWを研磨し、コンタクトホール内のWプラグ(栓)のみを残します。

- (B)配線層(メタル層)の形成

コンタクトの上には、ICの電源配線、あるいはチップ内のトランジスタ同士(信号線)をつなぐ水平方向の配線層が形成されます。

Step4: 配線層の形成(ダマシン法 : Damascene Process)

現在の先端プロセスでは、高性能・低抵抗な銅 (Cu) 配線が主流であり、デュアルダマシン法 (Dual Damascene)で形成されます。

- 溝(トレンチ)とビアホールの掘削:絶縁膜(Low-k膜)に、配線となるトレンチ(溝)と、下層のコンタクト(またはCu配線)へ接続するためのビアホールを、リソグラフィとエッチングで同時 (dual)に形成します。

- バリア層とシード層:溝とビアホールの内壁全体に、Cuの拡散を防ぐバリアメタルTaN, Taなど)を成膜し、その上にCuのシード層 (seed layer)を成膜します。

- 銅の埋め込み:電解めっきにより、トレンチとビアホール全体にCuを埋め込みます。

- CMP:余分なCuとバリア層をCMPで除去し、絶縁膜の中に埋め込まれたCuの配線とビア(垂直接続)が完成します。

さて、微細化が進み、信号線も多くなった近年のICでは、配線(メタル)は15層から20層にもなります。その形成するには、中間絶縁膜を堆積してvia holeを開け、金属を埋め込み、その上に金属配線を形成し、これを繰り返します。詳しくは第3回に記載しましたので、そちらを参照下さい。

1-1-5. 素子分離構造

ICには非常に多くのトランジスタが内蔵されています。これらの素子は通常、素子間の干渉などの影響を受けずに、設計通りに動作をする必要があります。そのために、ICには素子間の分離を行うための構造が組み込まれています。その構造は、微細化が進むにつれて大きな変遷を遂げてきました。

- (A)PN接合分離(PN Junction Isolation)

半導体の黎明期(今から40年ほど前)に使われていた手法で、基板上にP型とN型の領域を構成し逆バイアスすることで、接合部分に空乏層が広がり電流が流れにくい状態を作ります。構造としては簡単ですが、逆バイアス電圧が必要なのと接合部の寄生容量が大きくなることで、高速化には向かないなどの課題がありました。

- (B)LOCOS構造(Local Oxidation Of Silicon)

CMOS(Complementary Metal Oxide Semiconductor:PMOS, NMOSの相互補完)の導入とともに長期間に渡り主流となった分離技術です。

Si基板の分離したい部分に窒化シリコン(Si3N4)をマスクとして設け、高温で熱酸化を行うことで、厚い二酸化ケイ素 (SiO2) 膜を成長させ、これを分離膜としました。利点としては、比較的製造が容易で、高品質なSi/SiO2界面が得られます。しかしながら、Si3N4マスクの下にも酸化膜が横方向に潜り込んで成長するため、酸化膜の端が鳥のくちばし (bird’s beak) のような形状になり、トランジスタの有効面積を侵食しました。これが高密度化の限界をつくることになりました。

- (C)STI (Shallow Trench Isolation)

微細化が1um を大きく下回るようになると、より高密度な分離技術が必要になりました。そこで開発されたのがSTIという分離技術です。構造としては、ウェハ表面に深さ200~300nmのトレンチ(trench : 溝)を掘ります。トレンチの内壁を熱酸化してライナー酸化膜 (liner oxide film) を形成します。そして、CVDにより酸化膜を堆積してトレンチを埋めます。その後、余分な絶縁材料をCMP(Chemical Mechanical Polishing)により除去し、平坦化します。このような構造により、bird’s beak が無く平坦性も優れた微細な素子分離ができるため、現在の三次元的なトランジスタ構造にも引き続き用いられる技術となっています。

1-2. ムーアの法則

インテルの共同創業者の一人、Gordon Moore氏は、1965年、当時まだFairchild Semiconductor社の研究開発部門の責任者だった時、アメリカの電子技術専門誌「エレクトロニクス(Electronics)」誌の35周年記念号に寄稿する記事の執筆依頼を受けました。その時、求められた記事のテーマは、「電子部品の将来」でした。彼は、初期のトランジスタやICの製造データをプロットし、チップ上の部品数(トランジスタ数)が製造コスト効率を最大化するペースを調べました。その結果、チップ上に集積される部品数が、ある時期から指数関数的に増加している明確なトレンドを発見したのです。

彼は当初、「毎年、集積度が2倍になる」という予測を発表しました。これは、集積度が上がることで製品一台あたりの電子部品のコストが下がり続けることを示し、将来のコンピュータの時代を予見したものとなりました。その後1970年代半ばに、Moore氏は、この予測を修正して「およそ18か月から24か月で2倍」としました。1965年から1975年までの10年間の実際の集積度のデータ(特にインテルのメモリーチップ)を分析した結果、集積度の増加ペースはわずかに減速し、トランジスタの集積度が2倍になるのに、およそ2年かかっていることが確認されたためです。彼自身がこの修正を明確にしたのは、1975年にワシントンD.C.で開催されたIEDM(国際電子デバイス会議)での講演でした。ところで、ムーアの法則(Moore’s Law)は、自然科学の法則ではなく、技術の進歩を予測した経験則(トレンド)です。しかし、この予測があまりにも長期間にわたって正確だったため、半導体業界はこの「法則」を目標として開発を進め、結果的にその法則を実現し続けてきました。このような側面が、ムーアの法則の最大のユニークさと言えます。

現在、一般に最も広く知られている「18か月で2倍」という表現は、ムーア自身が提唱したものではなく、インテル社のエグゼクティブだったデイブ・ハウス(Dave House)氏によるものです。ハウス氏は、トランジスタ数の増加にトランジスタの動作速度の向上を合わせて考慮すると、チップ全体の性能が約18か月で2倍になると説明しました。この「性能」ベースの解釈が、特にビジネス界やメディアで広く使われるようになりました。ちなみに、ハウス氏は1970年代半ばから約20年間、当時のインテルの主要ないくつものマイクロプロセッサーの開発を牽引した人物で、「Intel Inside」のプロモーションにも関わっています。

2.要素技術

2-1. リソグラフィ

リソグラフィについては、第3回の中で詳しく説明しましたが、ここでは改めてフローに整理してみました。以下は典型的なリソグラフィ工程の流れです。なお、ここではポジレジストを想定しています。

- 1. クリーニング: ウェハ表面を清浄にする。

- 2. バリア層/密着促進剤塗布: フォトレジストの密着性を高める。

- 3. フォトレジスト塗布: ウェハを高速回転させながらレジストを均一に塗布。

- 4. プリベーク: レジスト中の溶剤を揮発させる。

- 5. 露光: フォトマスクを通して光を照射し、レジストの化学構造を変化させる。

- 6. ポストベーク: 露光後の化学反応を促進・安定化させる。

- 7. 現像: 変化した部分のレジストを溶解・除去し、パターンを形成。

- 8. 最終ベーク: レジストパターンを硬化させ、次のエッチング工程への耐性を高める。

このリソグラフィ工程が、半導体チップの性能を決定づける微細な回路パターンの「設計図」をウェハに刻み込む基盤となります。

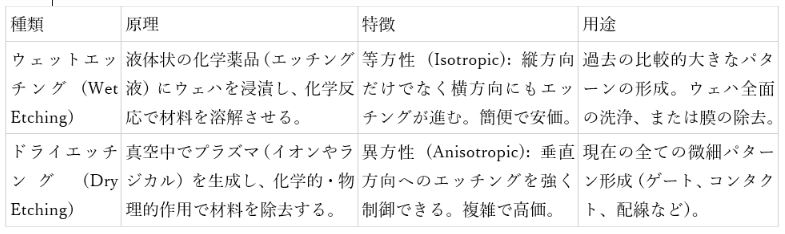

2-2. エッチング

エッチング技術は、大きく分けてウェットエッチングとドライエッチングの2種類あります。それぞれの特徴は次の通りです。

エッチング技術は、時代とともに変遷を遂げてきました。次に、その変遷の概要を記します。

2-2-1. 過去に使われていた手法(〜1 um:1ミクロンノード)

- (A) ウェットエッチング(wet etching)

微細化が進む前の時代は、リソグラフィの解像度も低かったため、ウェットエッチングが多用されました。

- 課題: 横方向の削れ (サイドエッチング: side etching)が発生し、パターンの線幅が設計より細くなってしまう(アンダーカット: undercut)。これが微細化の大きな障害となりました。

- (B) 初期のドライエッチング (プラズマエッチング: plasma etching)

微細化の要求が高まり、ドライエッチング (dry etching) が導入されましたが、まだ横方向のエッチングを完全に制御することは困難でした。

2-2-2. 近年の主流手法(サブミクロン以降: sub-micron)

微細化が進むにつれ、垂直方向への高い制御性(異方性:anisotropic)を持つドライエッチングが必須となりました。

- (A) RIE (Reactive Ion Etching: 反応性イオンエッチング)

現在の半導体製造において最も基本的なドライエッチング技術です。

- 原理: プラズマ中のラジカル(化学作用)とイオン(物理作用:垂直方向への衝突)の両方を利用することで、高い異方性を実現します。

- 重要性: ゲート電極の側壁を垂直に、あるいはコンタクトホールを深く真っ直ぐに掘るなど、微細加工の要となっています。

- (B) High-Density Plasma Etching (高密度プラズマエッチング)

さらなる微細化とアスペクト比(深さ/幅)の増大に対応するため、プラズマ密度を極限まで高めた技術(ICP: Inductively Coupled PlasmaやECR: Electron Cyclotron Resonanceなど)が使われます。

- 目的: 非常に深い穴や溝でも、高速かつ高精度に加工を可能にします。

- (C) Cu配線への適用(ダマシン法:method of processing damascene)

前述の通り、Cu(銅)はドライエッチングが難しいため、Cuをエッチングするのではなく、絶縁膜をエッチングして溝を作り、そこにCuを埋め込むダマシン法が主流となりました。

まとめると、エッチング技術は、微細化の進化そのものと言えます。単純な化学反応(ウェット)から、化学反応と物理的な衝突を高度に制御するプラズマ技術(ドライ)へと進化することで、現代の超精密なナノ回路の実現を可能にしたのです。

2-3. 洗浄

洗浄については、初期洗浄の項目で説明しましたが、中間工程での洗浄では前述の不純物の洗浄に加えて、フォトレジストの残渣の除去が重要な項目のひとつとなります。

次回は、引き続き半導体製造プロセスの詳細から製造後の測定・検査まで解説します。

無断転載・無断使用を禁じます。